硬件描述语言(verilog)和vhdl语言(vhdl)的区别

当谈到学习数字电子时,你可能会听到Verilog和VHDL。这两种语言都用于描述数字系统,但它们之间存在一些关键差异。在这篇博文中,我们将看看其中的一些差异。我们还将讨论为什么您可以选择一种语言而不是另一种语言。最后,您应该很好地了解Verilog和VHDL的独特之处,以及哪一种可能最适合您。

什么是硬件描述语言(verilog)?

Verilog是一种用于对电子系统建模的硬件描述语言(HDL)。它最常用于寄存器传输级(RTL)数字电路的设计和验证。Verilog还可以用于建模高级概念设计和系统级架构。Verilog基于Phil Moorby于1984年开发的验证语言(VL)。Verilog最初是作为一种封闭的专有语言创建的,后来根据Verilog-95规范作为开放标准发布。今天,Verilog仍然在工业中广泛使用,尽管它面临来自VHDL、SystemVerilog和Propel等其他HDL的竞争。

什么是vhdl语言(vhdl)?

VHDL是一种用于描述数字逻辑电路的硬件描述语言。VHDL可用于描述组合逻辑电路和顺序逻辑电路。VHDL代码可以使用VHDL模拟器进行模拟,该模拟器允许设计者在将其设计发送到制造之前对其进行测试。VHDL也用于合成,这是将VHDL代码转换为实际硬件的过程。与其他HDL相比,VHDL具有许多优点,包括其在高抽象级别上描述逻辑的能力以及其跨不同合成工具的可移植性。

硬件描述语言(verilog)和vhdl语言(vhdl)的区别

Verilog和VHDL是两种Verilog硬件描述语言。Verilog在北美更常用,而VHDL在欧洲更流行。Verilog的语法类似于C,而VHDL的语法更类似于Ada。Verilog比VHDL更容易学习。Verilog更适合于算法建模,而VHDL更适合于硬件结构建模。Verilog可以用于测试台,而VHDL不能。Verilog的模拟速度比VHDL快。Verilog可以合成为门,而VHDL不能。Verilog可以用于FPGA,而VHDL不能。Verilog不区分大小写,而VHDL区分大小写。Verilog没有标准库,而VHDL有标准库。Verilog允许在网络侧使用多个驱动程序,而VHDL不允许在网络端使用多个驱动器。

结论

在数字时代,Verilog和VHDL是两种最流行的硬件描述语言。它们用于建模和模拟电子系统。但它们之间有什么区别?让我们仔细看看。Verilog是由Gateway Design Automation Incorporated于1985年创建的专有语言。直到1995年,它才作为开源软件发布。另一方面,VHDL在1987年被IEEE标准化,此后多次修改。

- 发表于 2023-01-25 06:57

- 阅读 ( 14 )

- 分类:技术

你可能感兴趣的文章

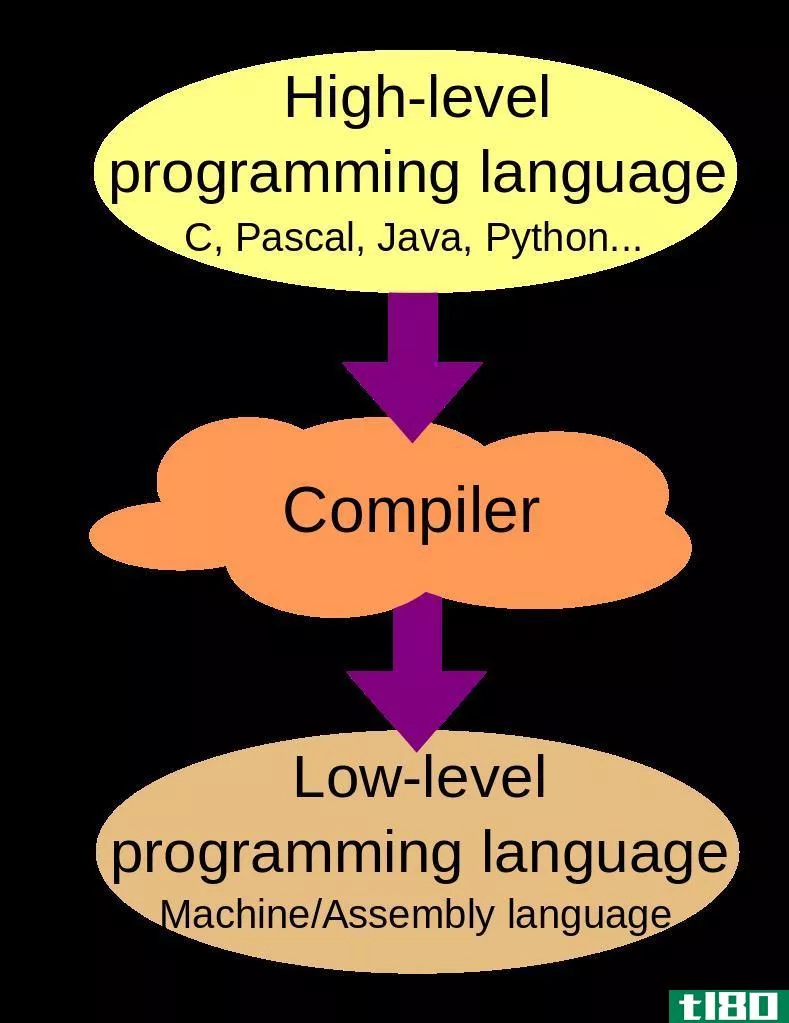

高级语言(high level language)和低级语言(low level language)的区别

...主要区别在于,高级语言是一种程序员友好的语言,它从硬件上提供高级抽象,而低级语言是一种对机器友好的语言,不提供或更少地从硬件抽象。高级语言可用于构建桌面、web和移动应用程序,低级语言可用于开发与硬件相关...

- 发布于 2020-10-23 20:12

- 阅读 ( 686 )

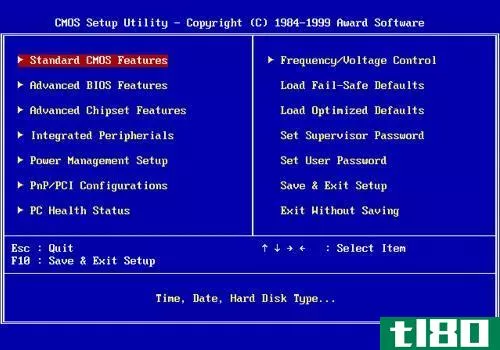

efi之间的差异(differences between efi)和bios(bios)的区别

...能是全新的。如果你有计算机相关的背景,并且对软件和硬件有一定的了解,那么你以前一定听过EFI和BIOS这个词。在这里,我们将强调两者之间的一些差异。但首先,让我们看看这些词是什么意思。 EFI是可扩展固件接口的缩写...

- 发布于 2021-06-24 15:13

- 阅读 ( 281 )

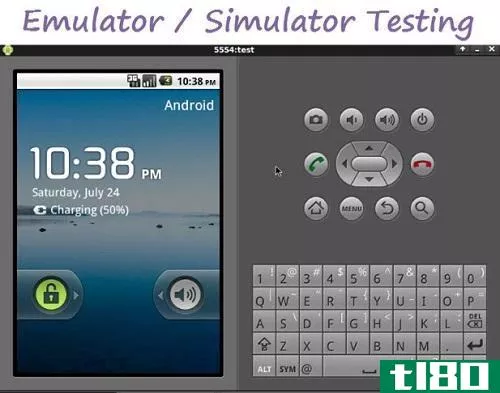

android仿真器的区别(differences between android emulator)和模拟器(simulator)的区别

...的。这种详尽的测试需要以某种方式模仿产品的特性。从硬件和软件两方面进行的模拟称为仿真器。模拟器可以测试源代码以及相关的硬件部分。我们甚至可以说仿真器可以从各个方面验证产品的正确性。 什么是模拟器(a simulato...

- 发布于 2021-06-25 00:52

- 阅读 ( 240 )

系统软件(system software)和应用软件(application software)的区别

...和应用软件的主要区别在于,系统软件有助于运行计算机硬件和应用软件,而应用软件有助于实现特定的用户需求。系统软件的例子有操作系统、语言处理器和设备驱动程序,而应用软件的例子有文字处理器、电子表格、演示软...

- 发布于 2021-06-30 17:44

- 阅读 ( 1011 )

描述的(descriptive)和规定语法(prescriptive grammar)的区别

描述性语法和规定性语法的主要区别在于,描述性语法描述了语言的使用方式,而规定性语法则解释了说话者应该如何使用语言。 语言学是研究语言及其结构的科学,包括语法、句法和语音的研究。关于语法的学习,主要有两...

- 发布于 2021-06-30 19:15

- 阅读 ( 2006 )

C(c)和嵌入式c(embedded c)的区别

...用编程语言,适合于开发各种应用程序,包括操作系统、硬件驱动程序、数据库等。尤其是在嵌入式系统开发中。 覆盖的关键领域 1.什么是C–定义,功能2.什么是嵌入式C–定义,功能3.C和嵌入式C的区别是什么–关键区别的比较...

- 发布于 2021-07-01 09:27

- 阅读 ( 316 )

硬件描述语言(verilog)和C(c)的区别

Verilog和C的主要区别在于Verilog是一种硬件描述语言,而C是一种高级通用编程语言。 Verilog是一种帮助设计和验证数字电路的语言。最新的稳定版本是ieee1364-2005。另一方面,C是一种流行的通用编程语言。常用于开发系统软件。简...

- 发布于 2021-07-01 09:36

- 阅读 ( 565 )

高密度脂蛋白(hdl)和软件语言(software language)的区别

...较 关键术语 C++,HDL,java,PHP,Python,软件语言,VHDL,Verilog 什么是高密度脂蛋白(hdl)? HDL代表硬件描述语言。HDL用来描述数字电路的行为。HDL语言由表达式、语句、控制结构等编程结构组成。这些语言构成了复杂电路、微处...

- 发布于 2021-07-01 11:34

- 阅读 ( 378 )

硬件描述语言(verilog)和系统验证日志(systemverilog)的区别

Verilog与SystemVerilog的主要区别在于Verilog是一种硬件描述语言,SystemVerilog是一种基于Verilog的硬件描述和硬件验证语言。 硬件描述语言(HDL)是一种用来描述电子电路结构和行为的计算机语言。硬件验证语言是一种编程语言,用于...

- 发布于 2021-07-01 22:23

- 阅读 ( 1774 )

模拟(simulation)和vhdl语言综合(synthesis in vhdl)的区别

...能,而综合用于编译VHDL并映射到FPGA等实现技术。 通常,硬件描述语言(HDL)是描述电子电路功能的语言。这些语言不同于常规编程语言。HDL有助于描述微处理器和触发器等数字系统。VHDL是一种流行的硬件描述语言。总之,VHDL...

- 发布于 2021-07-01 22:25

- 阅读 ( 683 )