闩锁vs触发器

锁存器和触发器是时序逻辑电路的基本组成部分,因此存储器。时序逻辑电路是一种数字电路,它不仅对当前输入做出响应,而且对电路的当前状态(或过去)做出响应。为了实现这一功能,电路必须能够将其状态保持为二进制信息。

有关闩锁的详细信息

存储设备的基本特性是,它应该能够将输出保持在一个固定的状态,直到它被指令改变为止。该功能由双稳态逻辑电路提供。简单地说,它有两个稳定状态:一个是设定状态,一个是复位状态。按照惯例,设置状态被视为1,重置状态被视为0。这种电路元件被称为闩锁;类似于将物体锁在固定位置的机械装置。

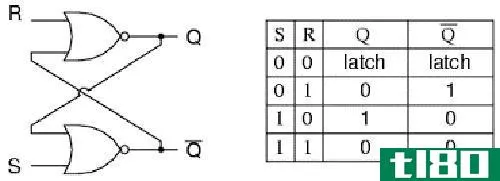

基本集复位锁存器(SR锁存器)是双稳态电路的最简单形式。JK和D锁存器是另外两种类型的锁存器。它们的操作很方便地用真值表表示。它是不同输入状态下所有可能结果的表格表示。

只要输入正确,基本锁存器就会改变其值。这就给控制大电路中存储在锁存器中的数据位带来了问题。通过将每个输入通过一个与门,可以对双稳态电路进行更多的控制。通过使用另一个信号控制与门,可以在需要的事件中允许输入。这个额外的输入称为启用,以这种方式配置的锁存器称为时钟锁存器或门控锁存器。通常,使能由时钟控制,时钟是具有理想的高(1)和低(0)状态间隔的数字信号。

对于时钟D锁存器,每当时钟处于高状态时,输出假定输入的每个高状态都是高状态。这种行为叫做透明。在某些应用中,闩锁的透明度是一个缺点。

更多关于人字拖

通常需要具备在特定时刻对输入进行采样并在内部保留值的能力。由于透明性,锁存器对时钟处于高状态时发生的任何事件都做出响应。作为解决方案,可以使用在时钟脉冲的上升沿或下降沿触发的双稳态电路。这些电路被称为触发器,与时钟脉冲的边缘同步。因此,触发器也被称为同步双稳态多谐振荡器电路。另一方面,锁存器是异步双稳态多谐振荡器电路。

与锁存器的操作相对应,还设计了SR、JK、D和T触发器。

闩锁和触发器有什么区别?

•闩锁是异步双稳态多谐振荡器电路,触发器是同步双稳态多谐振荡器电路。