硬件描述语言(verilog)和vhdl语言(vhdl)的区别

Verilog与VHDL的主要区别在于Verilog是基于C语言的,VHDL是基于Ada和Pascal语言的。

Verilog和VHDL都是硬件描述语言(HDL)。这些语言有助于描述数字系统的硬件,如微处理器和触发器。因此,这些语言不同于常规编程语言。VHDL是一种较老的语言,而Verilog是最新的语言。

覆盖的关键领域

1.什么是Verilog–定义,功能2.什么是VHDL–定义,功能3.Verilog和VHDL的区别是什么–主要区别的比较

关键术语

C语言,Verilog,VHDL

什么是硬件描述语言(verilog)?

Verilog是一种HDL(硬件描述语言)。Verilog的最新稳定版本是ieee1364-2005,Verilog是一种区分大小写的语言,只使用小写。它支持模拟。换言之,在构建真实系统之前,可以创建函数的模型并对其进行模拟。Verilog的基本语言是C。因此,熟悉C语言的程序员可以快速地学习Verilog。

模块是Verilog的基本构建块。它提供有关输入和输出端口的信息,并隐藏内部实现细节。module的语法如下。每个Verilog程序都以关键字“module”开始,以关键字“endmodule”结束。

模块(输入、输出);

<program logic>

终端模块

什么是vhdl语言(vhdl)?

VHDL是一种帮助描述数字系统中电路的HDL。VHDL中的硬件模块称为实体。语法如下。实体以“entity”开头,以“end”关键字结尾。

实体是

港口申报;

结束实体名称;

还有其他关键字,如In、Out、Inout和Buffer。In表示我们可以读取的端口。我们可以写的端口。Inout代表我们可以读写的端口。此外,可以对缓冲端口进行读写操作,并且只能有一个源。

VHDL中的建模主要有三种。它们如下。

数据流建模–并行信号表示通过实体的数据流

行为建模–将实体的行为表示为一组语句,以指定的顺序依次执行

结构化建模–将实体表示为一组相互关联的组件

硬件描述语言(verilog)和vhdl语言(vhdl)的区别

定义

Verilog是一种用于模拟电子系统的HDL,而VHDL是一种用于描述数字和混合信号系统(如现场可编程门阵列和集成电路)的电子设计自动化的HDL。

基本语言

Verilog与VHDL的主要区别在于Verilog是基于C语言的,VHDL是基于Ada和Pascal语言的。

区分大小写

此外,Verilog和VHDL的另一个区别是Verilog区分大小写,而VHDL不区分大小写。

引入时间段

Verilog是一种比VHDL更新的语言,因为Verilog是在1984年引入的,而VHDL是在1980年引入的。

复杂性

复杂性是Verilog和VHDL的另一个区别。VHDL比Verilog复杂。

结论

Verilog和VHDL是描述数字电子系统的两种硬件描述语言。Verilog与VHDL的主要区别在于Verilog是基于C语言的,VHDL是基于Ada和Pascal语言的。

引用

1.塔拉,迪帕克库马尔。Verilog中的Wire和Reg,1970年2月1日,此处提供。2。“Verilog:“维基百科,维基媒体基金会,1,2018,这里有。3。”VHDL:“维基百科,维基媒体基金会,6,2019,这里有。4。Verilog教程:Verilog简介,初学者点Shruti Jain,2017年8月13日,这里提供。 2、“Verilog”,维基媒体基金会,维基百科,12月1日, 3,“VHDL”,维基百科,维基媒体基金会,6月1日,2019 4.Verilog教程:Verilog简介,初学者点Shruti Jain,2017年8月13日,

- 发表于 2021-07-01 10:56

- 阅读 ( 146 )

- 分类:IT

你可能感兴趣的文章

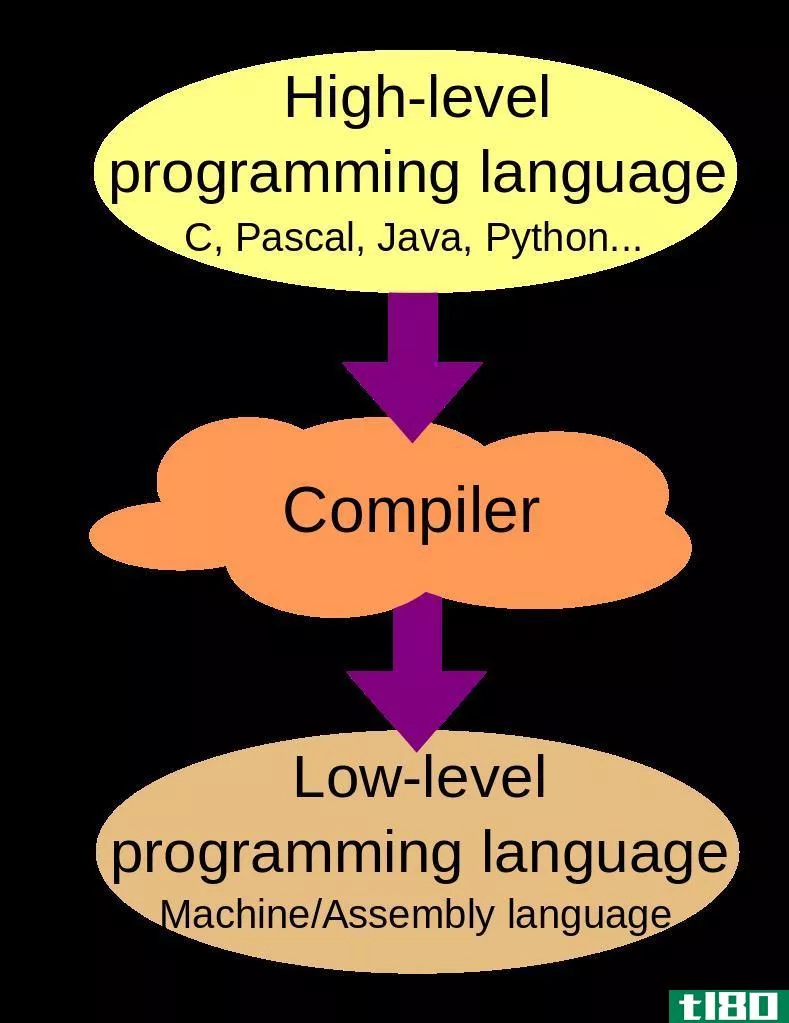

高级语言(high level language)和低级语言(low level language)的区别

...主要区别在于,高级语言是一种程序员友好的语言,它从硬件上提供高级抽象,而低级语言是一种对机器友好的语言,不提供或更少地从硬件抽象。高级语言可用于构建桌面、web和移动应用程序,低级语言可用于开发与硬件相关...

- 发布于 2020-10-23 20:12

- 阅读 ( 654 )

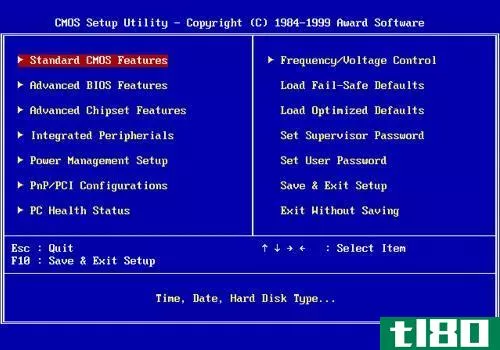

efi之间的差异(differences between efi)和bios(bios)的区别

...能是全新的。如果你有计算机相关的背景,并且对软件和硬件有一定的了解,那么你以前一定听过EFI和BIOS这个词。在这里,我们将强调两者之间的一些差异。但首先,让我们看看这些词是什么意思。 EFI是可扩展固件接口的缩写...

- 发布于 2021-06-24 15:13

- 阅读 ( 253 )

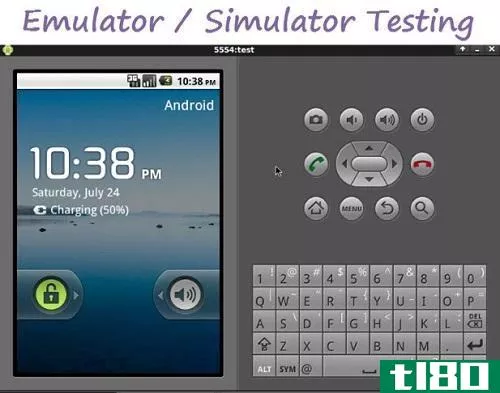

android仿真器的区别(differences between android emulator)和模拟器(simulator)的区别

...的。这种详尽的测试需要以某种方式模仿产品的特性。从硬件和软件两方面进行的模拟称为仿真器。模拟器可以测试源代码以及相关的硬件部分。我们甚至可以说仿真器可以从各个方面验证产品的正确性。 什么是模拟器(a simulato...

- 发布于 2021-06-25 00:52

- 阅读 ( 208 )

系统软件(system software)和应用软件(application software)的区别

...和应用软件的主要区别在于,系统软件有助于运行计算机硬件和应用软件,而应用软件有助于实现特定的用户需求。系统软件的例子有操作系统、语言处理器和设备驱动程序,而应用软件的例子有文字处理器、电子表格、演示软...

- 发布于 2021-06-30 17:44

- 阅读 ( 961 )

描述的(descriptive)和规定语法(prescriptive grammar)的区别

描述性语法和规定性语法的主要区别在于,描述性语法描述了语言的使用方式,而规定性语法则解释了说话者应该如何使用语言。 语言学是研究语言及其结构的科学,包括语法、句法和语音的研究。关于语法的学习,主要有两...

- 发布于 2021-06-30 19:15

- 阅读 ( 1953 )

C(c)和嵌入式c(embedded c)的区别

...用编程语言,适合于开发各种应用程序,包括操作系统、硬件驱动程序、数据库等。尤其是在嵌入式系统开发中。 覆盖的关键领域 1.什么是C–定义,功能2.什么是嵌入式C–定义,功能3.C和嵌入式C的区别是什么–关键区别的比较...

- 发布于 2021-07-01 09:27

- 阅读 ( 282 )

硬件描述语言(verilog)和C(c)的区别

Verilog和C的主要区别在于Verilog是一种硬件描述语言,而C是一种高级通用编程语言。 Verilog是一种帮助设计和验证数字电路的语言。最新的稳定版本是ieee1364-2005。另一方面,C是一种流行的通用编程语言。常用于开发系统软件。简...

- 发布于 2021-07-01 09:36

- 阅读 ( 538 )

高密度脂蛋白(hdl)和软件语言(software language)的区别

...较 关键术语 C++,HDL,java,PHP,Python,软件语言,VHDL,Verilog 什么是高密度脂蛋白(hdl)? HDL代表硬件描述语言。HDL用来描述数字电路的行为。HDL语言由表达式、语句、控制结构等编程结构组成。这些语言构成了复杂电路、微处...

- 发布于 2021-07-01 11:34

- 阅读 ( 330 )

硬件描述语言(verilog)和系统验证日志(systemverilog)的区别

Verilog与SystemVerilog的主要区别在于Verilog是一种硬件描述语言,SystemVerilog是一种基于Verilog的硬件描述和硬件验证语言。 硬件描述语言(HDL)是一种用来描述电子电路结构和行为的计算机语言。硬件验证语言是一种编程语言,用于...

- 发布于 2021-07-01 22:23

- 阅读 ( 1731 )

模拟(simulation)和vhdl语言综合(synthesis in vhdl)的区别

...能,而综合用于编译VHDL并映射到FPGA等实现技术。 通常,硬件描述语言(HDL)是描述电子电路功能的语言。这些语言不同于常规编程语言。HDL有助于描述微处理器和触发器等数字系统。VHDL是一种流行的硬件描述语言。总之,VHDL...

- 发布于 2021-07-01 22:25

- 阅读 ( 643 )