硬件描述语言(verilog)和系统验证日志(systemverilog)的区别

Verilog与SystemVerilog的主要区别在于Verilog是一种硬件描述语言,SystemVerilog是一种基于Verilog的硬件描述和硬件验证语言。

硬件描述语言(HDL)是一种用来描述电子电路结构和行为的计算机语言。硬件验证语言是一种编程语言,用于验证用硬件描述语言编写的电子电路。Verilog是HDL,SystemVerilog是HDL和HVL。总的来说,SystemVerilog是Verilog的超集。

覆盖的关键领域

1.什么是Verilog–定义,功能2.什么是SystemVerilog–定义,功能3.Verilog和SystemVerilog的区别–主要区别比较

关键术语

HDL、OOP、Verilog、SystemVerilog

什么是硬件描述语言(verilog)?

Verilog是一种硬件描述语言。它还有助于验证模拟电路和混合信号电路,并设计遗传电路。2009年,Verilog与SystemVerilog标准相结合。因此,Verilog目前是SystemVerilog的一部分。

Verilog的主要数据类型是Wire和Reg。线表示电路中连接门或模块的物理线。Reg保存从一个程序赋值到下一个程序赋值的值。

其他常用关键字如下。

Input–声明任务或模块的输入端口。

Output–声明任务或模块的输出端口。

Inout–声明任务或模块的双向端口。

Verilog支持不同层次的抽象。行为层描述了并发算法。寄存器传输级(RTL)通过操作和寄存器间的数据传输来解释电路的特性。此外,门级定义了逻辑链路及其时序属性。

什么是系统验证日志(systemverilog)?

SystemVerilog是一种基于Verilog的硬件描述和硬件验证语言,具有附加功能。它有助于建模、设计、模拟、测试和实现电子系统。此外,SystemVerilog主要应用于半导体和电子设计行业。

SystemVerilog中指定的两种数据类型是静态的和自动的。程序员在开始执行程序时创建静态变量。而且,该值在整个程序的生命周期内保持不变。此外,当在执行过程中为该值分配新值时,该值可能会更改。此外,自动变量是在程序执行到达变量范围时创建的。

SystemVerilog由三个新的程序块组成。这些有助于建立硬件模型。总梳有助于建立组合逻辑模型;always\u ff用于触发器,而always\u闩锁用于闩锁。HDL编译器或验证程序确保只发生所需类型的行为。此外,SystemVerilog包含的接口有助于减少连接模块之间端口名声明的冗余。

SystemVerilog的另一个重要用途是它支持面向对象编程。这些类支持单个继承模型。然而,程序员可以使用接口实现多个继承。他还可以实现类似于C++的多态性等概念。本地关键字和受保护的关键字有助于实现诸如封装等概念。默认情况下,类属性是公共的。此外,SystemVerilog还提供了一个自动垃圾收集器。

硬件描述语言(verilog)和系统验证日志(systemverilog)的区别

定义

Verilog是一种硬件描述语言(HDL),有助于对电子系统进行建模。相比之下,SystemVerilog是一种硬件描述,也是一种用于建模、设计、模拟、测试和实现电子系统的硬件验证语言。因此,这是Verilog和SystemVerilog的主要区别。

范式

另外,Verilog和SystemVerilog的另一个重要区别是Verilog支持结构化范式,而SystemVerilog支持结构化和面向对象范式。

ieee公司

Verilog标准化为IEEE 1364,SystemVerilog标准化为IEEE 1800。

文件扩展名

此外,Verilog的文件扩展名为.v或.vh,而SystemVerilog的文件扩展名为.sv和.svh。

影响

此外,Verilog和System Verilog之间的另一个区别是前者受C和FORTRAN的影响,而后者受Verilog、VHDL和C++的影响。

数据类型

Verilog支持Wire和Reg数据类型,SystemVerilog支持enum、struct、union、class和string等多种数据类型。因此,这也是Verilog和SystemVerilog之间的区别。

程序块

此外,Verilog有一个always块来实现组合逻辑和顺序逻辑,而SystemVerilog有always\u comb、always\u ff和always\u锁存程序块。

建设

虽然Verilog基于模块的层次结构,SystemVerilog是基于类的。

测试平台

此外,Verilog使用模块级testbench,而SystemVerilog使用基于类的testbench。

结论

Verilog与SystemVerilog的主要区别在于Verilog是一种硬件描述语言,SystemVerilog是一种基于Verilog的硬件描述和硬件验证语言。简而言之,SystemVerilog是Verilog的一个增强版本,具有附加功能。

引用

1、“Verilog”,维基百科,维基媒体基金会,3,2019,可在这里。2。“System Verilog”。维基百科,维基媒体基金会,2019年5月10日,可得。3.塔拉,Deepak Kumar。简介,1970年2月1日,在这里提供。 2,“System Verilog”,维基百科,维基媒体基金会,2019年5月10日, 3.塔拉,迪帕克库马尔。导言,1970年2月1日,

- 发表于 2021-07-01 22:23

- 阅读 ( 1732 )

- 分类:IT

你可能感兴趣的文章

xml(xml)和xsd公司(xsd)的区别

...这些不兼容的系统之间交换数据。XML是一种独立于软件和硬件的数据存储和传输方式。XML代表可扩展标记语言。XSD代表XML模式定义。XSD与XML相关。如果XML文档遵循正确的语法,那么它就是格式良好的文档。如果文档是根据XSD验证...

- 发布于 2020-10-19 03:20

- 阅读 ( 212 )

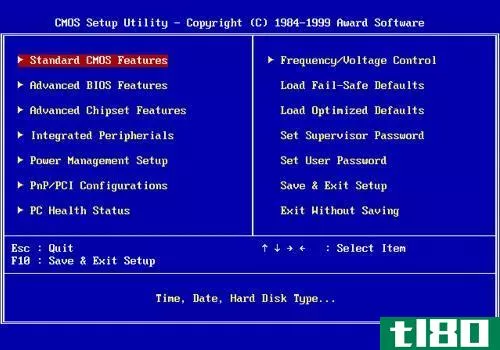

efi之间的差异(differences between efi)和bios(bios)的区别

...能是全新的。如果你有计算机相关的背景,并且对软件和硬件有一定的了解,那么你以前一定听过EFI和BIOS这个词。在这里,我们将强调两者之间的一些差异。但首先,让我们看看这些词是什么意思。 EFI是可扩展固件接口的缩写...

- 发布于 2021-06-24 15:13

- 阅读 ( 253 )

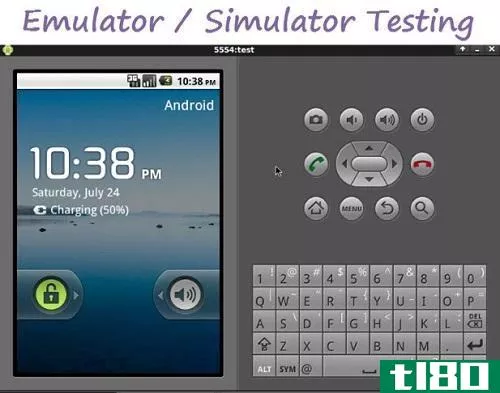

android仿真器的区别(differences between android emulator)和模拟器(simulator)的区别

...的。这种详尽的测试需要以某种方式模仿产品的特性。从硬件和软件两方面进行的模拟称为仿真器。模拟器可以测试源代码以及相关的硬件部分。我们甚至可以说仿真器可以从各个方面验证产品的正确性。 什么是模拟器(a simulato...

- 发布于 2021-06-25 00:52

- 阅读 ( 208 )

系统软件(system software)和应用软件(application software)的区别

...和应用软件的主要区别在于,系统软件有助于运行计算机硬件和应用软件,而应用软件有助于实现特定的用户需求。系统软件的例子有操作系统、语言处理器和设备驱动程序,而应用软件的例子有文字处理器、电子表格、演示软...

- 发布于 2021-06-30 17:44

- 阅读 ( 961 )

C(c)和嵌入式c(embedded c)的区别

...用编程语言,适合于开发各种应用程序,包括操作系统、硬件驱动程序、数据库等。尤其是在嵌入式系统开发中。 覆盖的关键领域 1.什么是C–定义,功能2.什么是嵌入式C–定义,功能3.C和嵌入式C的区别是什么–关键区别的比较...

- 发布于 2021-07-01 09:27

- 阅读 ( 282 )

硬件描述语言(verilog)和C(c)的区别

Verilog和C的主要区别在于Verilog是一种硬件描述语言,而C是一种高级通用编程语言。 Verilog是一种帮助设计和验证数字电路的语言。最新的稳定版本是ieee1364-2005。另一方面,C是一种流行的通用编程语言。常用于开发系统软件。简...

- 发布于 2021-07-01 09:36

- 阅读 ( 538 )

硬件描述语言(verilog)和vhdl语言(vhdl)的区别

Verilog与VHDL的主要区别在于Verilog是基于C语言的,VHDL是基于Ada和Pascal语言的。 Verilog和VHDL都是硬件描述语言(HDL)。这些语言有助于描述数字系统的硬件,如微处理器和触发器。因此,这些语言不同于常规编程语言。VHDL是一种较...

- 发布于 2021-07-01 10:56

- 阅读 ( 146 )

高密度脂蛋白(hdl)和软件语言(software language)的区别

...较 关键术语 C++,HDL,java,PHP,Python,软件语言,VHDL,Verilog 什么是高密度脂蛋白(hdl)? HDL代表硬件描述语言。HDL用来描述数字电路的行为。HDL语言由表达式、语句、控制结构等编程结构组成。这些语言构成了复杂电路、微处...

- 发布于 2021-07-01 11:34

- 阅读 ( 332 )

模拟(simulation)和vhdl语言综合(synthesis in vhdl)的区别

...能,而综合用于编译VHDL并映射到FPGA等实现技术。 通常,硬件描述语言(HDL)是描述电子电路功能的语言。这些语言不同于常规编程语言。HDL有助于描述微处理器和触发器等数字系统。VHDL是一种流行的硬件描述语言。总之,VHDL...

- 发布于 2021-07-01 22:25

- 阅读 ( 643 )

行为(behavioral)和verilog中的结构模型(structural model in verilog)的区别

Verilog中行为模型和结构模型的主要区别在于行为模型用算法描述系统,而结构模型用逻辑门等基本组件描述系统。 通常,计算机程序是一组允许CPU执行任务的指令。有各种各样的编程语言,如高级语言和低级语言。此外,还有...

- 发布于 2021-07-01 22:31

- 阅读 ( 741 )