模拟(simulation)和vhdl语言综合(synthesis in vhdl)的区别

VHDL中仿真和综合的主要区别在于仿真用于验证电路的功能,而综合用于编译VHDL并映射到FPGA等实现技术。

通常,硬件描述语言(HDL)是描述电子电路功能的语言。这些语言不同于常规编程语言。HDL有助于描述微处理器和触发器等数字系统。VHDL是一种流行的硬件描述语言。总之,VHDL有助于实现两个目标:仿真和综合。

覆盖的关键领域

1.什么是VHDL中的模拟–定义,功能2.什么是VHDL中的合成–定义,功能3.VHDL中模拟和合成的区别–关键区别的比较

关键术语

HDL,仿真,综合,VHDL

什么是vhdl仿真(simulation in vhdl)?

VHDL中的仿真或仿真程序有助于使用仿真模型来表示与设计接口的逻辑电路来测试逻辑设计。一组仿真模型就是一个试验台。

VHDL模拟器是一种事件驱动的模拟器。因此,每个事务都会添加到特定调度时间的事件队列中。此外,仿真结果也发生了变化。它们是语句执行和事件处理。语句执行是对触发语句的评估,而事件处理指处理队列中的事件。

什么是vhdl语言综合(synthesis in vhdl)?

综合是一个使用预先定义的构建块(如触发器、锁存器和逻辑门)的抽象描述来开发物理系统的过程。它从VHDL描述的电路模型创建门级网络表。最后,综合有助于将VHDL映射到FPGA和ASIC等技术。大多数FPGA**商提供免费工具来合成VHDL,以便与他们的芯片一起使用。

综合工具主要集中在FPGA和ASIC的逻辑设计上。他们不考虑敏感列表,因为他们关注于三个基本逻辑:组合逻辑、边缘敏感存储器(触发器和一些RAM)和电平敏感存储器(锁存器和一些RAM)。

此外,有些VHDL是不可合成的。因此,程序员可以编写VHDL代码,他可以模拟,但不能综合。对于可综合的设计描述,构造应该是综合工具可以接受的。

模拟(simulation)和vhdl语言综合(synthesis in vhdl)的区别

定义

仿真是用输入信号、输出信号和延迟来描述电路行为的过程。但是,综合是使用一组预定义的构建块从抽象描述构建物理系统的过程。因此,这描述了模拟和灵敏度之间的根本区别。

灵敏度列表

此外,simulation(simulator)使用敏感度列表来确定何时运行流程,而synthesis忽略敏感度列表。因此,这是模拟和灵敏度之间的另一个区别。

使用

最重要的是,这种用法导致了模拟和灵敏度之间的主要区别。仿真有助于验证电路的功能,而综合有助于转换VHDL描述以匹配目标技术。

结论

简而言之,程序员或电子设计师可以使用VHDL语言来测试描述逻辑电路的模型。在这里,VHDL涉及到实现两个主要目标;它们是电子设计的模拟和这些设计的综合。VHDL仿真与综合的主要区别在于仿真用于验证电路的功能,综合用于编译VHDL并映射到FPGA等实现技术。

引用

1,“VHDL”,维基百科,维基媒体基金会,2019年5月22日,可在这里。2.VHDL模拟和合成简介,可在此处获得。 2.VHDL仿真与综合简介,

- 发表于 2021-07-01 22:25

- 阅读 ( 643 )

- 分类:IT

你可能感兴趣的文章

线性的(linear)和会聚合成(convergent synthesis)的区别

...格形式的线性与收敛综合 5. 摘要 什么是线性综合(linear synthesis)? 线性合成是一种化学合成过程,其中一系列线性变换反应被用来将反应物或某些反应物转化为产品或多个产品。该合成过程包括生产目标产品的最长路线。因此,...

- 发布于 2020-10-03 02:00

- 阅读 ( 477 )

合成(synthesis)和逆合成(retrosynthesis)的区别

...列比较-表格形式的合成与反向合成 5. 摘要 什么是合成(synthesis)? 合成是有机化合物的构造。它是化学合成的一个特殊分支,是指有机合成。一般来说,有机化合物比无机化合物复杂。因此,这些有机化合物的合成过程也很复杂...

- 发布于 2020-10-14 12:01

- 阅读 ( 216 )

分析(analysis)和合成(synthesis)的区别

分析与综合 分析就像是演绎的过程,你把一个更大的概念分解成更小的概念。因此,分析将复杂的想法分解为更小的零碎概念,从而提出一个更好的理解。另一方面,综合通过解决它们有哪些共同点来解决对立与论文之间的冲...

- 发布于 2021-06-23 14:31

- 阅读 ( 379 )

游戏(games)和模拟(simulations)的区别

游戏与模拟 游戏和模拟是交互式多媒体,具有用户控制的动态元素。对于普通大众来说,游戏和模拟没有区别。 游戏是一个人可以在电脑游戏中玩的东西,而模拟是策略和技能与游戏的结合。 模拟和游戏在目的上有很大的不...

- 发布于 2021-06-23 17:41

- 阅读 ( 254 )

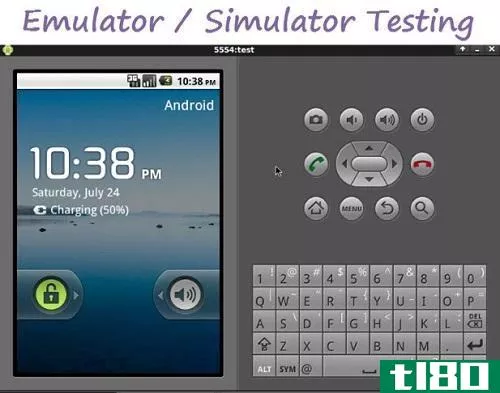

android仿真器的区别(differences between android emulator)和模拟器(simulator)的区别

...用的一切或技术,在这里我可以向您解释Android仿真器和模拟器之间的区别。 什么是机器人(an android)? 我们使用术语“Android”来表示各种各样的产品,比如**、Android手表、其他Android设备,甚至Android操作系统。如今,它已经成为...

- 发布于 2021-06-25 00:52

- 阅读 ( 208 )

硬件描述语言(verilog)和vhdl语言(vhdl)的区别

...05,Verilog是一种区分大小写的语言,只使用小写。它支持模拟。换言之,在构建真实系统之前,可以创建函数的模型并对其进行模拟。Verilog的基本语言是C。因此,熟悉C语言的程序员可以快速地学习Verilog。 模块是Verilog的基本...

- 发布于 2021-07-01 10:56

- 阅读 ( 145 )

高密度脂蛋白(hdl)和软件语言(software language)的区别

...本是ieee1364-2005,它是一种区分大小写的语言,允许实时模拟。这种语言的基本构造块称为模块。 VHDL–这种语言的基础语言是Ada和Pascal。它不区分大小写。VHDL中的硬件模块称为实体。通常,VHDL比Verilog复杂。 什么是软件语言(soft...

- 发布于 2021-07-01 11:34

- 阅读 ( 330 )

仿真器(emulator)和模拟器(simulator)的区别

仿真器和模拟器的主要区别在于,仿真器是一种软件或硬件,它使一个计算机系统能够与另一个系统类似地工作,而仿真器是一种软件或硬件,它可以模拟现实生活场景,提供所需的结果,而不会造成任何危险。 仿真器允许主...

- 发布于 2021-07-01 13:47

- 阅读 ( 496 )

硬件描述语言(verilog)和系统验证日志(systemverilog)的区别

...言(verilog)? Verilog是一种硬件描述语言。它还有助于验证模拟电路和混合信号电路,并设计遗传电路。2009年,Verilog与SystemVerilog标准相结合。因此,Verilog目前是SystemVerilog的一部分。 Verilog的主要数据类型是Wire和Reg。线表示电路...

- 发布于 2021-07-01 22:23

- 阅读 ( 1731 )

信号(signal)和vhdl中的变量(variable in vhdl)的区别

...in vhdl)? 变量是存储过程和子程序的局部信息的对象。在模拟过程中,可以通过变量赋值语句修改这些值。此外,变量声明可以包括单个或多个标识符、子类型指示和可选的全局静态表达式。例如,具有变量声明的代码如下所示...

- 发布于 2021-07-01 22:42

- 阅读 ( 750 )